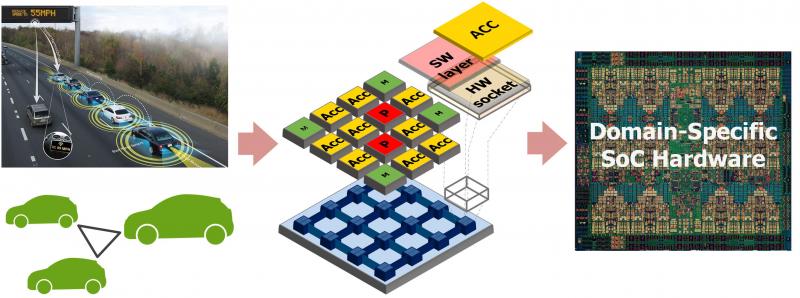

Compute-in-Memory for 3D Vision Processing

(DAC'24, ISLPED'23)In this project, we develop a domain-specific SoC for next generation smart, connected autonomous vehicles. To push the real-time performance and energy-efficiency, the SoC is designed with highly heterogeneous, including the general-purpose CPU processors, AI accelerators, and other specialized hardware accelerators. The SoC design adopts agile HLS design methodology, and based on the open-source Embedded Scalable Platform (ESP).

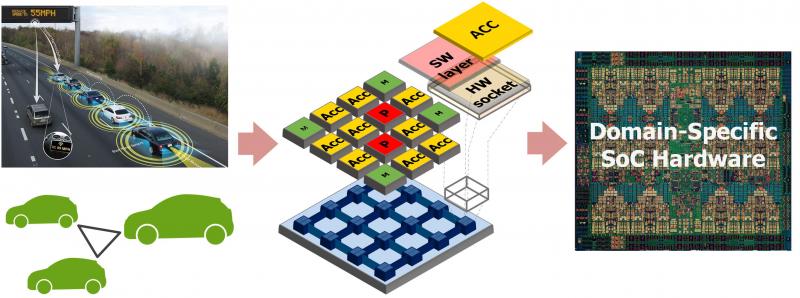

Efficiect Heterogeneous TinyML Architecture at Edge

(DAC'24, DAC'23)In this project, we develop a domain-specific SoC for next generation smart, connected autonomous vehicles. To push the real-time performance and energy-efficiency, the SoC is designed with highly heterogeneous, including the general-purpose CPU processors, AI accelerators, and other specialized hardware accelerators. The SoC design adopts agile HLS design methodology, and based on the open-source Embedded Scalable Platform (ESP).

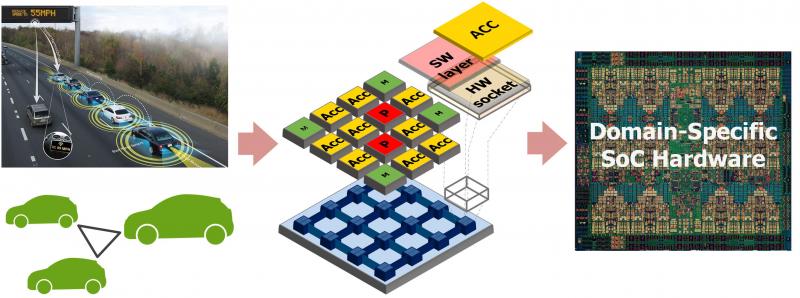

Agile-Designed Domain-Specific SoC Design and Methodology

(ISSCC'24, ISSCC'23, ICCAD'22, ESSCIRC'22)In this project, we develop a domain-specific SoC for next generation smart, connected autonomous vehicles. To push the real-time performance and energy-efficiency, the SoC is designed with highly heterogeneous, including the general-purpose CPU processors, AI accelerators, and other specialized hardware accelerators. The SoC design adopts agile HLS design methodology, and based on the open-source Embedded Scalable Platform (ESP).